Device for integrated and distributed control and management of intelligent buildings and flats

Czech Technical University in Prague, Faculty of Electrical Engineering

Czech national patent

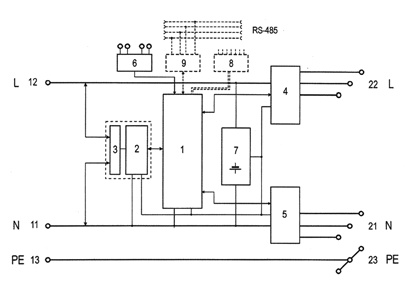

The device represents an effective solution for intelligent buildings and flats. It is based on IP/PLC communication protocols and provides management and control using network distribution cabling. The centre of the device is a microcomputer (1) communicating with other devices of this type and with the Internet via a communication module (2) and a frequency filter (3). The module (4) of the switching elements is controlled by the phase conductor (L) of the connected network elements, while the module (5) for measuring the currents flowing into the neutral conductor (N) provides information on their consumption. The module (6) for sensing the state of the control elements allows connection of a driver, such as switches, buttons or potentiometers of the network distribution cabling. The source (7) powers the device and its accumulator supports the basic functions at network outages. The input/output interface (8) allows connection of various sensors, camera sensors, memory elements and wireless modules. The data can be processed locally, in collaboration with other elements according to the design, and/or distributed to the Internet. The device can be connected to an RS-485 bus used in standard building and flat control networks using a converter (9).

System for implementation of a dispersion table

CESNET, z. s. p. o.

Czech Technical University in Prague, Faculty of Information Technology

Czech national patent

European patent

United States Patent

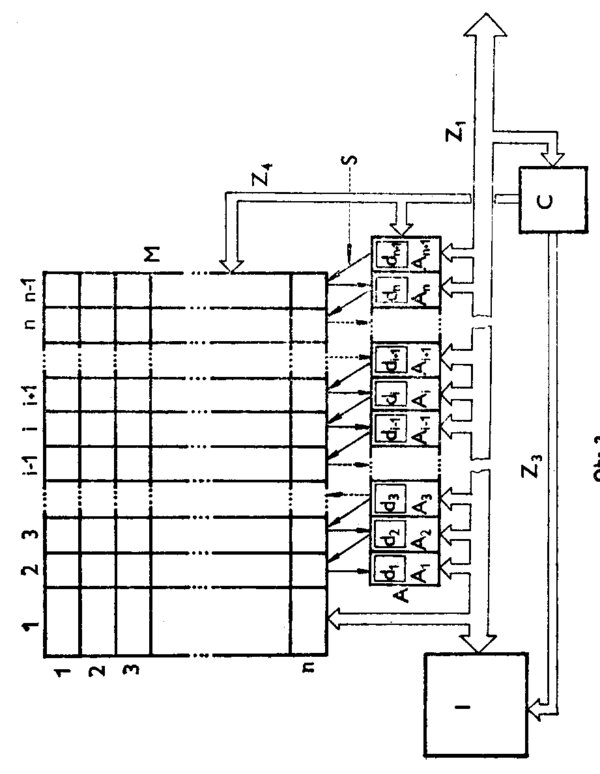

The solution submitted enables implementation of a dispersion table, for example for compression algorithms, with fast initialization and, at the same time, small demands on system resources. The main parts of the solution are one or more base blocks (1), a corresponding number of masking blocks (20), the counter (14), the address divider (15), the demultiplexer (18) and the multiplexer (22). Each base block (1) includes the flag register memory (4) implemented as a LUT table. In the normal operating mode, the address of the entire symptom system is divided by the address divider (15) into a part connected simultaneously to all the base blocks (1) and to a part that the demultiplexer (18) uses to enable writing in one of the base blocks (1). The masking blocks (20) together with the multiplexer (22) select the contents of the addressed base block (1). In the initialization mode, the counter (14) successively creates all the addresses on the base block (1) inputs for setting the flag register memory (4).

Circuit arrangement for integrated control and management in service networks of smart buildings

Czech Technical University in Prague, Faculty of Electrical Engineering

Czech national patent

Deutsches Patent

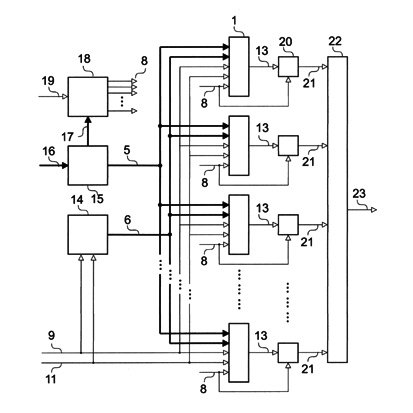

The present invention covers a device for efficient solution and project of service network of smart buildings, which is based on sharing a harness that is primary used for making local computer networks of Ethernet, i.e. four-pair cables UTP Cat.5, optionally Cat.6. The device comprises a central processor (1), which supports any program needful for the device function. Interface (2) 802.3 for communication by IEEE 802.3c protocol interconnects the device with two pairs (1-2 a 3-6) of the UTP cable normally used by the Ethernet technology. Interface (3) of the RS-485 bus uses in common Ethernet local networks and devices used therein such as routers, switches, servers, memory centers, printers, and other unused pairs (5-4) of the UTP cables as a bus complying with the standard RS-485 in the synchronous communication (peer-to-peer) operational mode. The described device can also be provided with a suitable input/output module (4), making it possible to operate with optional own sensors or own control elements, and/or it can locally provide for the user information about the state and to ensure control of the device itself, as well as through the mediation of the central processor (1) and the IEEE 802.3 interface (2) for the communication through the protocol IEEE 802.3c and the interface (3) of the RS-485 bud of arbitrary other device of the service network, and/or it can serve for processing optical information of a camera sensor, i.e. to provide storage of data, its evaluation, for example detection of movement and its preparation for transmission to the central processor of the service network computer or to a remote indicator. A power supply unit (5) for other parts of the device uses the free pairs (7-8) of the UTP cables and makes it possible to feed sensors and control elements of the busses RS-485 as well as mutual backup of other devices. The connection of contacts between the interface (3) of the RS-485 bus and the two pairs (1-2) and (3-6) makes it possible to use the cables connected to connectors (B, C) of the RJ-45 type and unused for Ethernet transmission for additional bus according to RS-485 in the asynchronous communication mode of operation.

Circuit arrangement for generating multiplicative inversion above final GF (p) body

Czech Technical University in Prague, Faculty of Electrical Engineering

Czech national patent

United States Patent 7574469

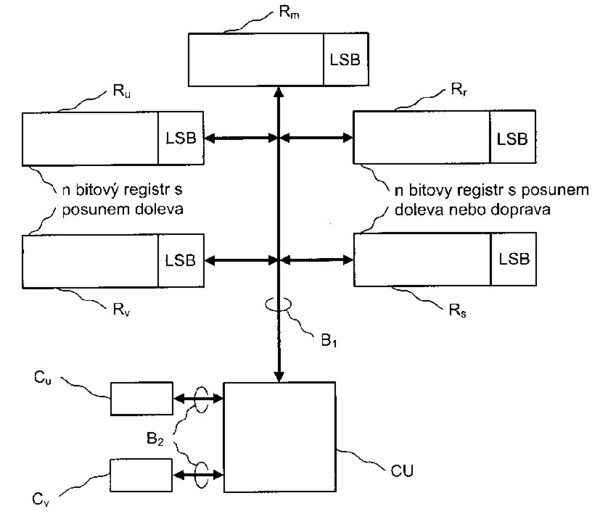

In the present invention, there is disclosed a circuit arrangement for generating efficient multiplicative inversion above final GF (p) body wherein p represents a prime number, i.e. by generating modular inversion. The circuit is adapted to carry out operations by binary way within the process of generation of the modular inversion relative to the least possible number of addition, subtraction and shift operations. The process implemented by the circuit here proposed removes redundant operations after conversion of odd and negative values that are carried out in so far employed processes. For this purpose there is used a representation of negative numbers in an additional code, shift of values to left in the control section of Euclid algorithm and novel definition of monitoring and control conditions serving for execution of the process. Minimizing the number of adding and subtracting operations is desirable in case of calculation with large numbers that occur in cryptography.

Processor unit connection

Institute of Physics CEFV SAS, Bratislava

Czechoslovak national patent