Zařízení pro integrované a distribuované řízení a správu inteligentních budov a bytů

České vysoké učení technické v Praze, Fakulta elektrotechnická

Český národní patent

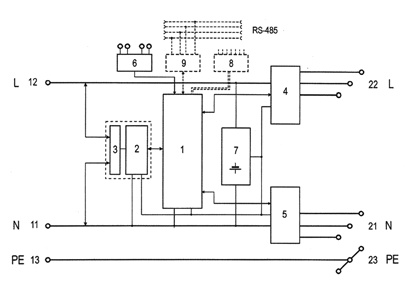

Zařízení představuje efektivní řešení sítě služeb inteligentních budov a bytů. Opírá se o komunikaci protokoly IP/PLC a zajišťuje správu a ovládání s využitím kabeláže síťových rozvodů. Centrem zařízení je mikropočítač (1) komunikující s dalšími zařízeními tohoto typu a s Internetem prostřednictvím komunikačního modulu (2) a kmitočtového filtru (3). Modul (4) spínacích prvků ovládá fázový vodič (L) připojených síťových prvků, modul (5) pro měření proudů tekoucích do nulového vodiče (N) poskytuje informace o jejich spotřebě. Modul (6) pro snímání stavu ovládacích prvků dovoluje připojit ovladače, jako jsou vypínače, tlačítka nebo potenciometry kabeláží síťového rozvodu. Zdroj (7) zařízení napájí a jeho akumulátor podporuje základní funkce při výpadcích sítě. Vstupně/výstupní rozhraní (8) dovoluje připojit různé senzory, kamerové snímače, paměťové prvky a bezdrátové moduly. Data je možné zpracovat lokálně, ve spolupráci s dalšími prvky podle návrhu a/nebo distribuovat do Internetu. Převodníkem (9) lze zařízení připojit ke sběrnici RS-485 využívané v sítích standardního řízení budov a bytů.

Systém pro realizaci rozptylovací tabulky

CESNET, z. s. p. o.

České vysoké učení technické v Praze, Fakulta informačních technologií

Český národní patent

Evropský patent

United States Patent

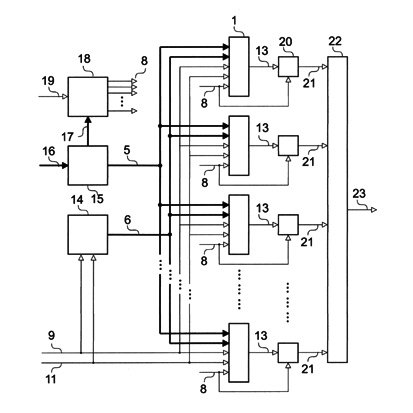

Předkládané řešení umožňuje realizovat rozptylovací tabulku, například pro činnost kompresních algoritmů, s rychlou inicializací a současně s malými nároky na systémové prostředky. Hlavními částmi řešení jsou jeden nebo více základních bloků (1), odpovídající počet maskovacích bloků (20), čítač (14), adresní rozdělovač (15), demultiplexor (18) a multiplexor (22). Každý základní blok (1) obsahuje paměť (4) příznakového registru implementovaného jako tabulka LUT. V normálním provozním režimu je adresa celého systému příznaků rozdělena adresním rozdělovačem (15) na část připojenou současně do všech základních bloků (1) a na část, kterou demultiplexor (18) využije pro povolení zápisu do jednoho ze základních bloků (1). Maskovací bloky (20) spolu s multiplexorem (22) vybírají obsah adresovaného základního bloku (1). V režimu inicializace vytváří čítač (14) postupně všechny adresy na vstupech základních bloků (1) pro nastavení pamětí (4) příznakových registrů.

Zapojení pro integrované řízení a správu v sítích služeb inteligentních budov

České vysoké učení technické v Praze, Fakulta elektrotechnická

Český národní patent

Deutsches Patent

Návrhem je kryto zařízení pro efektivní řešení a projekt sítě služeb inteligentních budov, které se opírá o sdílení kabeláže primárně užívané pro výstavbu lokálních počítačových sítí Ethernetu, tedy o čtyřpárové kabely UTP Cat.5 případně Cat.6. Zařízení obsahuje centrální procesor (1), který podporuje libovolný program potřebný pro funkci zařízení. Rozhraní (2) 802.3 pro komunikaci protokolem IEEE 802.3c propojuje zařízení s dvojicí párů (1-2 a 3-6) UTP kabelu standardně využívaných technologií Ethernetu. Rozhraní (3) sběrnice RS-485 využívá v běžných lokálních sítích Ethernetu a v nich používaných zařízeních jako jsou směrovače/routery, přepínače/switche, servery, paměťová centra, tiskárny, ale i další, nepoužívané páry (5-4) UTP kabelů jako sběrnici splňují standard RS-485 v režimu synchronní (peer-to-peer) komunikace. Popisované zařízení může být také vybaveno vhodným vstupně/výstupním modulem (4), který dovoluje pracovat s případnými vlastními senzory nebo vlastními ovládacími prvky, a/nebo může uživateli lokálně poskytnout informaci o stavu a zajistit ovládání jak vlastního zařízení, tak prostřednictvím centrálního procesoru (1) a rozhraní (2) IEEE 802.3 pro komunikaci protokolem IEEE 802.3c a rozhraní (3) sběrnice RS-485 libovolného jiného zařízení sítě služeb, a/nebo může sloužit pro zpracování optických informací kamerového snímače, tedy zajistit ukládání dat, jejich vyhodnocení, např. detekci pohybu a přípravu pro přenos na centrální počítač sítě služeb nebo na vzdálený indikátor. Napájecí zdroj (5) pro ostatní části zařízení využívá nepoužívané páry (7-8) kabelů UTP a dovoluje i napájení senzorů a ovládacích prvků sběrnic RS-485 a vzájemné zálohování jiných zařízení. Propojení kontaktů mezi rozhraním (3) sběrnice RS-485 a dvojicí párů (1-2) a (3-6) dává možnost použít kabely připojené ke konektorům (B, C) typu RJ-45 a nevyužité pro přenos Ethernetu pro přídavnou sběrnici podle RS-485 v režimu asynchronní komunikace.

Zapojení pro generování multiplikativní inverze nad konečným tělesem GF(p)

České vysoké učení technické v Praze, Fakulta elektrotechnická

Český národní patent

United States Patent 7574469

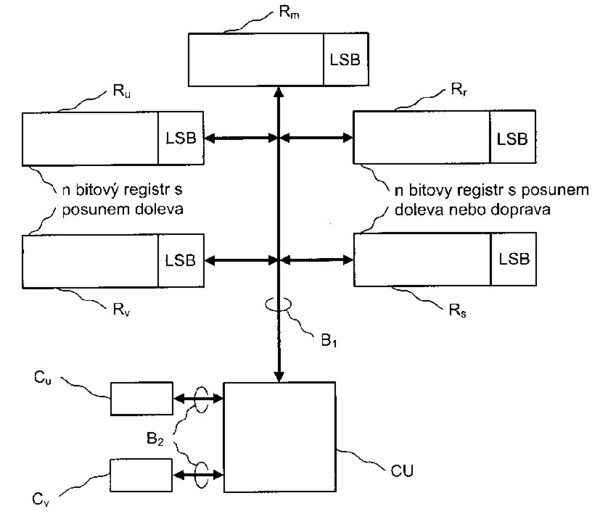

Podstata vynálezu spočívá ve vytvoření zapojení pro efektivní generování multiplikativní inverze nad konečným tělesem GF(p), kde p je prvočíslo, tj. generováním modulární inverze. Zapojení je upraveno pro binární vykonávání operací v procesu generování modulární inverze, a to vzhledem k co nejmenšímu počtu operací sčítání, odečítání a posuvu. Postup realizovaný navrženým zapojením odstraňuje redundantní operace pro konverzi lichých a záporných hodnot, které jsou prováděny u dosavadních postupů. K tomu se využívá reprezentace záporných čísel v doplňkovém kódu, posun hodnot doleva v řídicí části rozšířeného Euklidova algoritmu a nová definice hlídacích a řídicích podmínek provádění postupu. Minimalizování počtu operací sčítání a odečítání je žádoucí v případě počítání s velkými čísly, která se vyskytují v kryptografii.

Zapojenie procesorovej jednotky

Fyzikálny ústav CEFV SAV, Bratislava

Československý národní patent

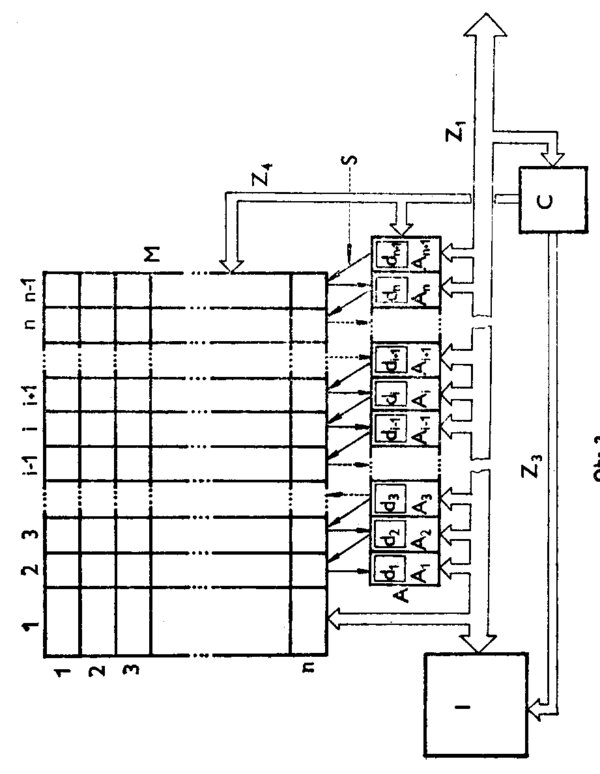

Účelom zapojenia procesorovej jednotky je presné riešenie sústavy lineárnych rovníc v oblasti zvolenej zvyškovej triedy. Uvedeného účelu sa dosiahne výpočtom inverznej matice v modulovej aritmetike, ktorý sa vykonáva v aritmetickej jednotke (A) v spolupráci s pamäťovým maticovým polom (M), blokom (I) tvorby modulových inverzných a negovaných čísel a blokom (C) riadiacej logiky. K riešeniu sústavy lineárnych rovníc v obore reálnych čísel je potrebných viacero procesorových jednotiek (P1 až Pm), ktoré pracujú synchrónne v súčinnosti s riadiacou jednotkou (R) a hositeľským počítačom (H). Zapojenie procesorovej jednotky môže nájsť široké uplatnenie pri riešení sústav lineárnych rovníc vo všetkých oblastiach vedy a techniky.